Sự phát triển của ngành công nghiệp bán dẫn trong hơn năm thập kỷ qua luôn xoay quanh trục chính là Định luật Moore, với mục tiêu không ngừng thu nhỏ kích thước bóng bán dẫn để tăng mật độ và hiệu suất. Tuy nhiên, khi các nút thắt vật lý ở quy mô nanomet trở nên khắc nghiệt, việc tiếp tục thu nhỏ theo chiều ngang (2D scaling) không còn mang lại lợi ích kinh tế và hiệu năng tối ưu. Trong bối cảnh đó, ngành công nghiệp đã chuyển hướng mạnh mẽ sang tích hợp theo chiều dọc (3D integration), nơi các con chip không còn đứng đơn lẻ mà được xếp chồng lên nhau để tạo thành các hệ thống phức hợp. Trung tâm của cuộc cách mạng này chính là công nghệ liên kết (bonding), đặc biệt là liên kết lai (hybrid bonding) – một kỹ thuật then chốt cho phép đạt được mật độ kết nối cực cao, băng thông khổng lồ và hiệu suất năng lượng vượt trội. Báo cáo này sẽ đi sâu vào phân tích bản chất vật lý, quy trình chế tạo của các công nghệ liên kết, đồng thời thực hiện một nghiên cứu so sánh chi tiết giữa ba kiến trúc bộ nhớ 3D NAND hàng đầu thế giới hiện nay: Xtacking của YMTC, CBA của Kioxia và V-NAND của Samsung.

Sự Tiến hóa của Công nghệ Liên kết trong Sản xuất Bán dẫn

Trong quy trình đóng gói linh kiện bán dẫn, liên kết (bonding) là quá trình kết nối cơ học và điện tử giữa các thành phần khác nhau, chẳng hạn như giữa chip với đế (substrate), chip với chip (die-to-die), hoặc giữa các tấm wafer với nhau (wafer-to-wafer). Sự tiến hóa của công nghệ này phản ánh trực tiếp nhu cầu về mật độ đầu vào/đầu ra (I/O) ngày càng tăng.

Công nghệ Vi điểm lồi (Micro-bumps) và Giới hạn Vật lý

Truyền thống, việc xếp chồng các lớp chip 3D, đặc biệt là trong bộ nhớ băng thông cao (HBM), dựa trên công nghệ vi điểm lồi (micro-bumps). Đây là quá trình sử dụng các điểm lồi bằng đồng (Cu) được phủ một lớp chì hàn (solder) mỏng để tạo kết nối giữa các lớp. Kích thước của các micro-bumps đã giảm dần từ mức 40 \mu m xuống 20 \mu m và hiện tại đang tiến gần ngưỡng 10 \mu m.

Tuy nhiên, khi khoảng cách giữa các điểm kết nối (pitch size) thu nhỏ xuống dưới 10 \mu m, công nghệ micro-bumps đối mặt với những thách thức không thể vượt qua. Đầu tiên là hiện tượng tràn chì hàn gây ngắn mạch giữa các chân tín hiệu khi mật độ quá dày đặc. Thứ hai, sự hình thành các lớp hợp kim gian kim (IMC) giữa đồng và thiếc dẫn đến điện trở cao hơn, làm tăng độ trễ tín hiệu và tiêu thụ điện năng không mong muốn. Cuối cùng, sự hiện diện của lớp micro-bump tạo ra một khoảng trống vật lý khoảng 30 \mu m giữa các die, đòi hỏi phải sử dụng vật liệu dưới (underfill) để bảo vệ, điều này không chỉ làm tăng độ dày của gói chip mà còn cản trở khả năng tản nhiệt theo chiều dọc.

Bản chất của Hybrid Bonding (Liên kết lai)

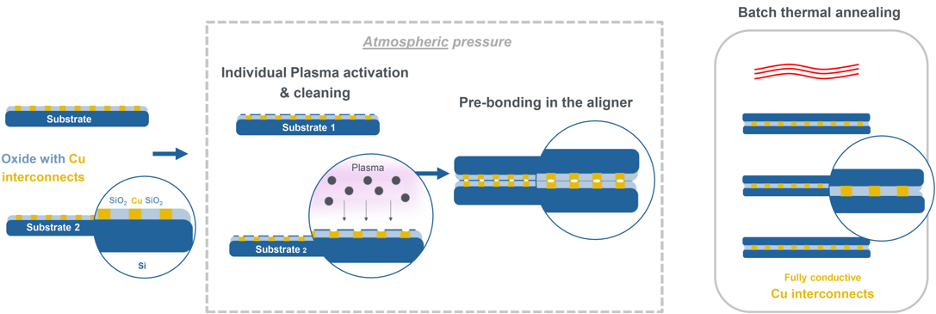

Hybrid bonding, hay còn được gọi là liên kết trực tiếp đồng-đồng (Cu-Cu direct bonding), đại diện cho một sự thay đổi mô hình hoàn toàn. Thay vì sử dụng các điểm lồi trung gian, công nghệ này cho phép các die hoặc wafer kết nối trực tiếp với nhau thông qua một bề mặt siêu phẳng bao gồm cả vật liệu điện môi và các miếng đệm đồng. Tên gọi "hybrid" (lai) xuất phát từ việc quá trình này kết hợp đồng thời hai loại liên kết: liên kết phân tử giữa các lớp điện môi (thường là SiO2 hoặc SiCN) và liên kết kim loại giữa các bề mặt đồng.

Cơ chế của hybrid bonding dựa trên hiện tượng khuếch tán chất rắn của các nguyên tử đồng. Tại giao diện liên kết, đồng và điện môi được đánh bóng đạt tới độ phẳng ở cấp độ nguyên tử. Khi hai bề mặt được tiếp xúc ở nhiệt độ phòng, lực hút Van der Waals giữa các lớp điện môi tạo ra sự gắn kết ban đầu. Quá trình ủ nhiệt (annealing) sau đó sẽ kích hoạt sự giãn nở nhiệt của đồng; vì hệ số giãn nở nhiệt của đồng cao hơn điện môi, đồng sẽ trồi lên lấp đầy các khoảng trống nhỏ nhất và tạo ra sự thẩm thấu nguyên tử xuyên qua ranh giới, hình thành một kết nối kim loại đồng nhất và cực kỳ bền vững.

Nguồn tham khảo:

Phân loại các Phương pháp thực hiện Hybrid Bonding

Tùy thuộc vào yêu cầu của thiết kế và quy mô sản xuất, hybrid bonding có thể được thực hiện qua ba quy trình chính, mỗi loại có những ưu và nhược điểm riêng biệt về chi phí, sản lượng và độ tin cậy.

-

Wafer-to-Wafer (W2W): Đây là phương pháp phổ biến nhất trong sản xuất 3D NAND và cảm biến hình ảnh (CIS). Hai tấm wafer hoàn chỉnh được căn chỉnh với độ chính xác nanomet và liên kết với nhau trước khi được cắt thành các con chip riêng lẻ. W2W mang lại sản lượng cao nhất và độ chính xác căn chỉnh tốt nhất (có thể đạt mức dưới 100 nm), nhưng nó yêu cầu các chip trên hai wafer phải có kích thước giống hệt nhau và không cho phép loại bỏ các chip lỗi trước khi bonding, điều này có thể ảnh hưởng đến hiệu suất thu hoạch (yield) tổng thể.

-

Die-to-Wafer (D2W): Các chip riêng lẻ (đã được kiểm tra là tốt - Known Good Die) được gắn lên một tấm wafer đích. Phương pháp này linh hoạt hơn W2W vì cho phép kết hợp các con chip có kích thước khác nhau từ các nút công nghệ khác nhau (dị thể). Tuy nhiên, tốc độ xử lý của D2W thấp hơn do phải thực hiện gắp-đặt từng chip, và yêu cầu khắt khe hơn về việc kiểm soát hạt bụi trong quá trình cắt wafer.

-

Die-to-Die (D2D): Hai con chip riêng lẻ được liên kết với nhau. Đây là phương thức ít phổ biến nhất trong sản xuất hàng loạt do hiệu suất thấp, nhưng lại rất hữu ích cho các mẫu thử nghiệm nghiên cứu hoặc các hệ thống tùy chỉnh cao cấp.

Cơ chế Kỹ thuật và Quy trình Chế tạo Hybrid Bonding

Để đạt được một liên kết hybrid thành công, quy trình chế tạo đòi hỏi sự kiểm soát nghiêm ngặt đối với các bước xử lý bề mặt và điều kiện môi trường. Ngay cả một hạt bụi kích thước 1 \mu m cũng có thể gây ra hiện tượng không liên kết trên một diện tích lớn, dẫn đến lỗi toàn bộ con chip.

Quy trình Damascene và Chuẩn bị Bề mặt

Quy trình bắt đầu bằng việc tạo ra các hố (cavities) trên lớp điện môi bằng phương pháp khắc ion phản ứng (RIE). Sau đó, một lớp rào cản (barrier) như TaN và một lớp hạt giống (seed) đồng được lắng đọng bằng phương pháp CVD hoặc ALD để ngăn đồng khuếch tán vào silicon. Đồng sau đó được lấp đầy vào các hố bằng kỹ thuật mạ điện.

Bước quan trọng nhất trong toàn bộ quy trình là Đánh bóng Hóa cơ học (CMP). CMP không chỉ làm phẳng bề mặt mà còn phải tạo ra một độ lõm cực nhỏ (copper dishing) – thường là vài nanomet – của các miếng đệm đồng so với bề mặt điện môi. Nếu độ lõm quá sâu, đồng sẽ không thể chạm vào nhau khi giãn nở nhiệt; nếu đồng trồi lên quá cao, nó sẽ ngăn cản các lớp điện môi tiếp xúc hoàn toàn, để lại các khoảng trống chứa khí.

Kích hoạt Plasma và Bonding ở Nhiệt độ Phòng

Trước khi bonding, bề mặt được làm sạch bằng sóng megasonic và kích hoạt bằng plasma (thường là khí N2 hoặc Argon). Quá trình này tạo ra các nhóm hydroxyl (-OH) hoạt động trên bề mặt điện môi. Khi hai wafer được đưa lại gần nhau, một "làn sóng liên kết" (bonding wave) sẽ lan tỏa từ tâm ra rìa wafer, tạo ra liên kết hydro ban đầu giữa các bề mặt điện môi. Độ chính xác căn chỉnh trong bước này là cực kỳ quan trọng; đối với các pitch dưới 1 \mu m, sai số căn chỉnh phải được kiểm soát dưới 100 nm.

Ủ nhiệt và Khuếch tán Nguyên tử

Giai đoạn cuối cùng là ủ nhiệt ở nhiệt độ từ 300 độ C đến 400 độ C trong vài giờ. Trong giai đoạn này, các liên kết hydro chuyển đổi thành các liên kết cộng hóa trị Si-O-Si bền vững, tạo ra độ bền cơ học cho cấu trúc. Đồng thời, áp suất sinh ra từ sự giãn nở nhiệt buộc các bề mặt đồng phải tiếp xúc khăng khít, kích hoạt quá trình khuếch tán nguyên tử qua ranh giới hạt, tạo nên một kết nối điện liên tục. Việc sử dụng các vật liệu điện môi tiên tiến như SiCN thay vì SiO2 đang được nghiên cứu rộng rãi vì SiCN có năng lượng liên kết cao hơn, khả năng ngăn chặn khuếch tán đồng tốt hơn và độ ổn định nhiệt vượt trội.

Cuộc Cách mạng Kiến trúc 3D NAND: Sự dịch chuyển sang Hybrid Bonding

Sự phát triển của 3D NAND đã trải qua ba giai đoạn kiến trúc chính, mỗi giai đoạn giải quyết những thách thức về mật độ và chi phí theo những cách khác nhau. Việc hiểu rõ các kiến trúc này là tiền đề để so sánh các giải pháp của YMTC, Kioxia và Samsung.

1. Kiến trúc Cổ điển: CMOS Next to Array (CNA)

Trong những thế hệ đầu tiên của 3D NAND, các mạch logic ngoại vi (peripheral circuitry) – bao gồm các bộ giải mã hàng, bộ khuếch đại cảm biến và mạch I/O – được đặt nằm cạnh mảng ô nhớ (memory array) trên cùng một bề mặt wafer. Cách tiếp cận này đơn giản về mặt quy trình nhưng cực kỳ kém hiệu quả về diện tích, vì mạch ngoại vi có thể chiếm tới 20-30% diện tích toàn bộ con chip.

2. Kiến trúc Đơn wafer: CMOS Under Array (CuA/COP/PUC)

Để tối ưu hóa không gian, các nhà sản xuất đã chuyển sang đặt mạch ngoại vi xuống dưới mảng bộ nhớ. Kiến trúc này được biết đến với nhiều tên gọi tùy theo hãng sản xuất:

-

Micron/Intel: CMOS Under Array (CuA).

-

Samsung: Cell Over Periphery (COP).

-

SK Hynix: Periphery Under Cell (PUC), hay còn gọi là "4D NAND".

Ưu điểm lớn nhất của CuA là tiết kiệm diện tích và giảm chi phí vì toàn bộ linh kiện được chế tạo trên một tấm wafer duy nhất. Tuy nhiên, nó tạo ra một thách thức nhiệt học rất lớn: mảng ô nhớ 3D NAND yêu cầu các quy trình xử lý nhiệt độ cao (như ủ kênh polysilicon) để đảm bảo hiệu suất lưu trữ, nhưng nhiệt độ cao này lại có thể làm hỏng hoặc làm thay đổi đặc tính của các bóng bán dẫn logic đã được chế tạo bên dưới. Điều này buộc các kỹ sư phải đánh đổi: hoặc giảm nhiệt độ xử lý mảng nhớ (làm giảm chất lượng ô nhớ), hoặc chấp nhận hiệu suất logic thấp hơn.

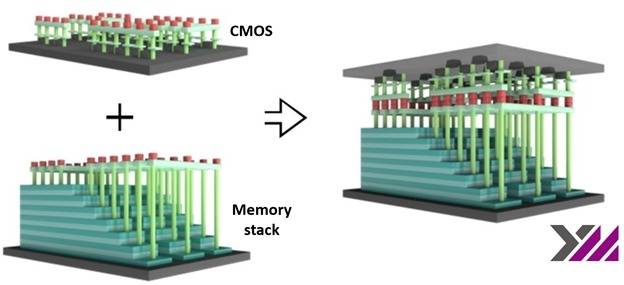

3. Kiến trúc Hai wafer: Liên kết Lai (Hybrid Bonding)

Đây là đỉnh cao hiện tại của công nghệ 3D NAND, nơi mảng ô nhớ và mạch ngoại vi được chế tạo trên hai tấm wafer hoàn toàn riêng biệt. Sau khi hoàn tất, hai wafer được úp vào nhau và liên kết bằng kỹ thuật hybrid bonding W2W. Kiến trúc này cho phép tối ưu hóa độc lập cả hai thành phần: mạch logic có thể sử dụng các nút công nghệ tiên tiến nhất để đạt tốc độ cao, trong khi mảng nhớ có thể được xử lý nhiệt ở mức tối ưu mà không lo ngại ảnh hưởng đến logic.

Phân tích So sánh: YMTC Xtacking vs. Kioxia BiCS vs. Samsung V-NAND

Mỗi nhà sản xuất đã chọn một thời điểm và phương thức khác nhau để áp dụng hybrid bonding vào lộ trình sản phẩm của mình, dẫn đến sự khác biệt đáng kể về mật độ, hiệu suất và vị thế trên thị trường.

YMTC Xtacking: Kẻ Tiên phong và Người giữ bằng sáng chế

YMTC (Yangtze Memory Technologies Co.) là công ty đầu tiên thương mại hóa kiến trúc hybrid bonding cho 3D NAND dưới thương hiệu Xtacking vào năm 2018. Quyết định này ban đầu được xem là một sự mạo hiểm vì chi phí sản xuất hai wafer cao hơn, nhưng nó đã giúp YMTC nhanh chóng rút ngắn khoảng cách công nghệ với các đối thủ lâu đời.

-

Cơ chế Xtacking: YMTC sản xuất wafer mảng nhớ và wafer logic riêng biệt. Wafer logic thường được sản xuất trên các tiến trình logic tiêu chuẩn, cho phép tốc độ I/O nhanh hơn nhiều so với các mạch ngoại vi được chế tạo trong môi trường bộ nhớ. Xtacking hiện đã phát triển đến thế hệ 4.x.

-

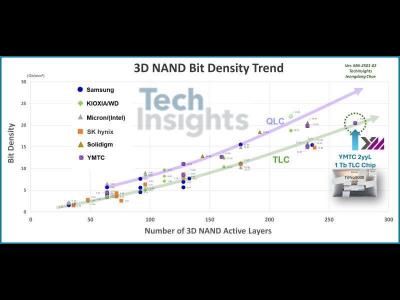

Lợi thế Mật độ: Do toàn bộ mạch ngoại vi nằm hoàn toàn bên dưới mảng nhớ và các kết nối giữa chúng được thực hiện qua hàng tỷ vi thông (VIA) theo chiều dọc, diện tích chip được giảm thiểu tối đa. Thế hệ Xtacking 4.x trên chip 294 lớp đã đạt được mật độ bit vượt ngưỡng 20 Gb/mm^{2}, một kỷ lục trong ngành tại thời điểm ra mắt.

-

Vị thế Pháp lý: YMTC hiện nắm giữ một danh mục bằng sáng chế khổng lồ về hybrid bonding (hơn 1.240 bằng), bao gồm cả các công nghệ cốt lõi mua lại từ Xperi. Điều này tạo ra một rào cản lớn cho các đối thủ khác khi muốn chuyển sang kiến trúc tương tự.

Kioxia BiCS: CBA (CMOS Bonded to Array)

Kioxia và Western Digital, sau nhiều năm trung thành với kiến trúc CuA, đã chuyển sang hybrid bonding từ thế hệ BiCS8 với tên gọi CBA (CMOS Bonded to Array). CBA về cơ bản có triết lý tương đồng với Xtacking: tách biệt và tối ưu hóa.

-

Cải tiến Hiệu suất: Với CBA, Kioxia đã có thể áp dụng quy trình xử lý nhiệt độ cao cho mảng nhớ BiCS8 mà không làm suy giảm hiệu suất của transistor CMOS. Kết quả là dòng điện ô nhớ (cell current) tăng 35% và tốc độ giao diện đạt 3.2 - 3.6 Gbps.

-

Mật độ kỷ lục trên BiCS10: Kioxia đã công bố lộ trình cho thế hệ thứ 10 với 332 lớp, dự kiến đạt mật độ bit kinh ngạc 36.4 Gb/mm^{2} và tốc độ 4.8 Gbps. Đây là minh chứng cho thấy hybrid bonding cho phép các nhà sản xuất tăng mật độ bit mà không nhất thiết phải chạy đua quá mức về số lượng lớp (layers), thay vào đó là thu nhỏ kích thước ô nhớ theo cả chiều ngang và dọc.

Samsung V-NAND: Sự Chuyển dịch bắt buộc từ V10

Samsung là hãng giữ vững kiến trúc COP (đơn wafer) lâu nhất. Thế hệ V9 của họ với 286 lớp vẫn sử dụng COP và đạt được những thành công nhất định về chi phí. Tuy nhiên, Samsung đã xác định rằng COP sẽ chạm tới giới hạn vật lý ở mức khoảng 400 lớp.

-

Tại sao Samsung phải đổi? Khi số lớp chồng lên nhau quá cao, ứng suất vật lý từ hàng trăm lớp màng mỏng sẽ gây ra sự biến dạng wafer và áp lực cực lớn lên các mạch logic nằm dưới cùng, làm giảm độ tin cậy và hiệu suất.

-

Bước ngoặt V10: Bắt đầu từ thế hệ V10 (dự kiến 420-430 lớp), Samsung sẽ chính thức chuyển sang hybrid bonding W2W. Việc chuyển đổi này không chỉ nhằm giải quyết vấn đề ứng suất mà còn để đáp ứng nhu cầu tốc độ giao diện cực cao cho các trung tâm dữ liệu AI, với mục tiêu đạt 5.6 Gbps. Một điểm đáng chú ý là Samsung đã ký thỏa thuận cấp phép bằng sáng chế với YMTC để sử dụng công nghệ hybrid bonding cho V10.

Bảng So sánh Tổng thể các Kiến trúc 3D NAND

Nguồn dữ liệu:

Ý nghĩa của Hybrid Bonding đối với Hiệu năng Hệ thống và Ứng dụng AI

Trong kỷ nguyên của Trí tuệ nhân tạo, khả năng lưu trữ không chỉ nằm ở dung lượng mà còn ở tốc độ di chuyển dữ liệu. Hybrid bonding đóng vai trò là "siêu xa lộ" cho dữ liệu.

Tối ưu hóa Đặc tính Điện và Nhiệt

Việc thay thế các vi điểm lồi bằng liên kết đồng trực tiếp mang lại những cải thiện vượt trội về mặt vật lý :

-

Giảm trở kháng: Đồng có điện trở suất cực thấp. Liên kết trực tiếp giảm điện trở đường dẫn tín hiệu hơn 50%, giúp giảm tiêu thụ điện năng và nhiệt tỏa ra.

-

Cải thiện Tản nhiệt: Đồng là chất dẫn nhiệt tuyệt vời. Trong cấu trúc xếp chồng, giao diện hybrid bonding đóng vai trò như một kênh dẫn nhiệt hiệu quả từ các lớp giữa ra ngoài, giảm nhiệt trở của toàn bộ gói chip từ 15% đến 30%. Điều này cực kỳ quan trọng đối với các ổ cứng SSD hiệu năng cao PCIe Gen 5 và Gen 6 vốn thường gặp vấn đề quá nhiệt.

Kết luận

Công nghệ liên kết lai (hybrid bonding) đã chứng minh được vị thế là một trong những đổi mới quan trọng nhất của ngành bán dẫn trong thập kỷ này. Từ một giải pháp kỹ thuật nhằm vượt qua giới hạn của micro-bumps, nó đã trở thành "xương sống" kiến trúc cho toàn bộ lộ trình phát triển của 3D NAND và các hệ thống tính toán hiệu năng cao.

Qua sự so sánh giữa YMTC, Kioxia và Samsung, chúng ta thấy rõ một xu hướng hội tụ: tất cả các con đường đều dẫn tới hybrid bonding khi số lớp NAND vượt ngưỡng 400. YMTC với Xtacking đã đi trước một bước; Kioxia với CBA đang tối ưu hóa mật độ bit; trong khi Samsung với V10 đang chuẩn bị bứt phá về hiệu năng AI.

Danh sách nguồn tham khảo hữu ích cho website:

-

Kioxia - Công nghệ CBA cho BiCS FLASH thế hệ 8: https://www.kioxia.com/en-jp/rd/technology/cba.html

-

SemiEngineering - Giải thích chi tiết về quy trình chế tạo Hybrid Bonding: https://semiengineering.com/making-hybrid-bonding-better/

-

Applied Materials - Cấu tạo giải phẫu 3D NAND và lộ trình mở rộng: https://www.appliedmaterials.com/us/en/semiconductor/markets-and-inflections/memory/3d-nand.html

-

TechInsights - Phân tích đột phá Xtacking 4.0 của YMTC: https://www.techinsights.com/blog/ymtc-xtacking40-breaking-new-ground-3d-nand-technology

-

Tom's Hardware - Samsung công bố V-NAND thế hệ 10 với Hybrid Bonding: https://www.tomshardware.com/pc-components/ssds/samsung-unveils-10th-gen-v-nand-400-layers-5-6-gt-s-and-hybrid-bonding

Nguồn trích dẫn

1. Hybrid Bonding Basics – What is Hybrid Bonding? - Brewer Science, https://www.brewerscience.com/what-is-hybrid-bonding/ 2. Hybrid Bonding: The New Precision Bottleneck in Advanced Packaging - Basler AG, https://www.baslerweb.com/en/learning/semicon-hybrid-bonding/ 3. Cost and Yield Comparison of Wafer-to-Wafer, Die-to-Wafer, and Die-to-Die Bonding - IMAPSource Proceedings, https://imapsource.org/article/57531-cost-and-yield-comparison-of-wafer-to-wafer-die-to-wafer-and-die-to-die-bonding.pdf 4. Bridging Performance and Yield: The Evolving Role of Interconnect Technologies in HBM, https://ontoinnovation.com/resources/bridging-performance-and-yield-the-evolving-role-of-interconnect-technologies-in-hbm/ 5. Emerging Trends and Key Markets in 2.5D and 3D Semiconductor Packaging | SemiWiki, https://semiwiki.com/forum/threads/emerging-trends-and-key-markets-in-2-5d-and-3d-semiconductor-packaging.21396/ 6. Cu–Cu Bonding for 3D IC and Hybrid Integration: A Comprehensive Guide - LoveChip, https://www.lovechip.com/blog/cu-cu-bonding-process-methods 7. Hybrid Bonding Set to Transform the Semiconductor Industry - EE Times, https://www.eetimes.com/revamping-the-semiconductor-industry-with-hybrid-bonding/ 8. Role of 3D Cu-Cu Hybrid Bonding in Powering Future HPC & AI Products - IDTechEx, https://www.idtechex.com/en/research-article/role-of-3d-cu-cu-hybrid-bonding-in-powering-future-hpc-and-ai-products/30902 9. Wafer-to-wafer hybrid bonding | imec, https://www.imec-int.com/en/articles/wafer-wafer-hybrid-bonding-pushing-boundaries-400nm-interconnect-pitch 10. What is CMOS directly Bonded to Array (CBA) Technology? | KIOXIA ..., https://www.kioxia.com/en-jp/rd/technology/cba.html 11. Making Hybrid Bonding Better - Semiconductor Engineering, https://semiengineering.com/making-hybrid-bonding-better/ 12. Hybrid Bonding Technology Market Insights & Growth Outlook 2025–2032, https://www.congruencemarketinsights.com/report/hybrid-bonding-technology-market 13. A Cost and Yield Analysis of Wafer-to-wafer Bonding - ResearchGate, https://www.researchgate.net/publication/283767990_A_Cost_and_Yield_Analysis_of_Wafer-to-wafer_Bonding 14. Development of CMOS Directly Bonded to Array(CBA) Technology for 3D Flash Memory | KIOXIA - Japan (English), https://www.kioxia.com/en-jp/rd/technology/topics/topics-64.html 15. Scaling up 3D NAND Flash architecture - GOODRAM Industrial, https://goodram-industrial.com/en/news/scaling-up-3d-nand-flash-architecture/ 16. 3D NAND Hits 400+ Layers with Hybrid Bonding - ALLPCB, https://www.allpcb.com/allelectrohub/3d-nand-hits-400-layers-with-hybrid-bonding 17. Comparison: Latest 3D NAND Products from YMTC, Samsung, SK ..., https://www.techinsights.com/blog/comparison-latest-3d-nand-products-ymtc-samsung-sk-hynix-and-micron 18. Upcoming New 3D NAND TLC Devices: Samsung 176L & 238L, SK hynix 176L, KIOXIA/WD 162L | TechInsights, https://www.techinsights.com/blog/upcoming-new-3d-nand-tlc-devices-samsung-176l-238l-sk-hynix-176l-kioxiawd-162l 19. Advancing Flash Memory Architecture with CBA Technology | KIOXIA Blog, http://blog-us.kioxia.com/post/2026/01/13/advancing-flash-memory-architecture-with-cba-technology 20. Overview of new technologies applied to BiCS FLASH™ generation 8 - KIOXIA, https://www.kioxia.com/en-jp/rd/technology/topics/topics-66.html 21. High-density 3D flash memory using high-precision wafer bonding brings new value to storage | KIOXIA, https://www.kioxia.com/en-jp/business/topics/bics-cba-202407.html 22. Did Samsung Just Endorse YMTC's Xtacking? - The Memory Guy Blog, https://thememoryguy.com/did-samsung-just-endorse-ymtcs-xtacking/ 23. Kioxia and WD's BiCS 8 tech takes YMTC route: Separately fabs NAND control logic and cell stacks - Blocks and Files, https://www.blocksandfiles.com/flash/2023/03/31/kioxia-and-wds-bics-8-tech-takes-ymtc-route-separately-fabs-nand-control-logic-and-cell-stacks/1600089 24. YMTC 2yy-layered 3D NAND — the Highest TLC Bit Density Ever from the Market!, https://library.techinsights.com/public/sectioned-blog-viewer/0c9b5f26-ceb8-4df9-aca2-b7aec7777fa9 25. Kioxia achieve with 332-layer 3D NAND flash memory ... ..., https://www.hugdiy.com/news/global-flash-memory-breakthrough-332-layer-3d-nand-sets-new-industry-benchmark/ 26. Kioxia's new 10th gen 332-layer 4.8 GB/s 3D NAND flash is 33% faster than its 8th gen ICs, https://www.tomshardware.com/tech-industry/kioxias-new-10th-gen-332-layer-4-8-gb-s-3d-nand-flash-is-33-percent-faster-than-its-8th-gen-ics 27. Samsung developing 400-plus-layer 3D NAND - Blocks and Files, https://www.blocksandfiles.com/data-management/2024/12/04/samsung-developing-400-plus-layer-3d-nand/1603230 28. Samsung Aims for 1000-Layer NAND by 2030, Begins Wafer Bonding at 400 Layers, https://www.techpowerup.com/333155/samsung-aims-for-1-000-layer-nand-by-2030-begins-wafer-bonding-at-400-layers 29. Samsung unveils 10th Gen V-NAND: 400+ layers, 5.6 GT/s and hybrid bonding, https://www.tomshardware.com/pc-components/ssds/samsung-unveils-10th-gen-v-nand-400-layers-5-6-gt-s-and-hybrid-bonding 30. News Posts matching 'YMTC' - TechPowerUp, https://www.techpowerup.com/news-tags/YMTC